Planning a data platform, analytics system, or AI solution? Our team can help design scalable architectures and deliver production-ready solutions tailored to your business.

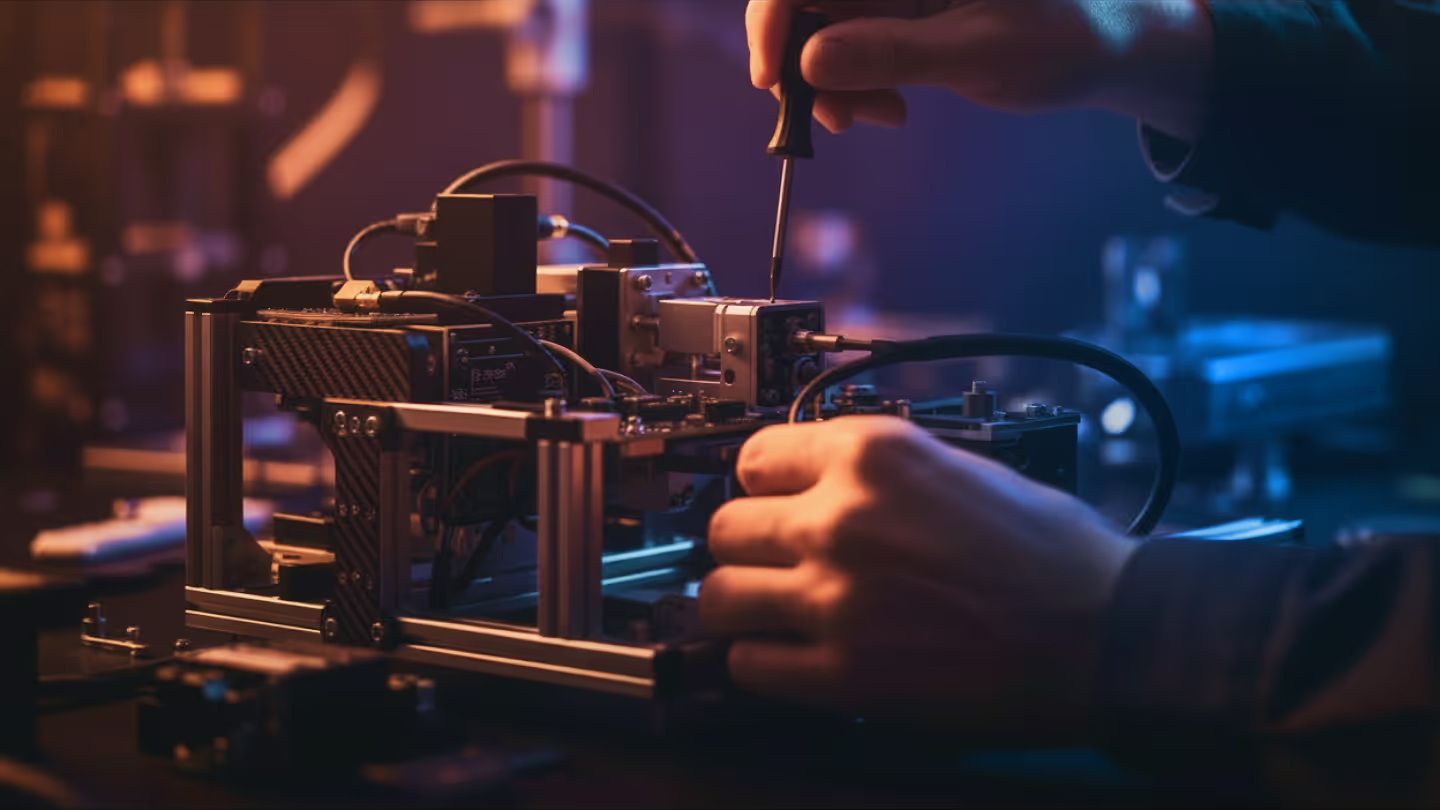

Client context

A technology company focused on aerospace solutions, developing advanced systems for navigation, communication, and real-time data processing where precision and reliability are critical.

The challenge

Accurate time measurement is a foundational requirement for aerospace navigation systems, directly affecting positioning accuracy, synchronization, and system reliability.

The client needed an FPGA-based IP core capable of delivering high-precision timing while operating within the constraints of hardware resources and real-time performance.

At the same time, the system had to meet strict reliability expectations, including data validation, error detection, and stable operation across varying environmental conditions. Ensuring compatibility with standard interfaces and different FPGA platforms added another layer of complexity.

What it took to deliver results

To meet aerospace requirements, the solution needed to:

- achieve very high accuracy in time measurement

- implement statistical calculations directly in hardware

- ensure reliable data validation and error detection

- support standardized interfaces for system integration

- operate efficiently across different FPGA platforms

- maintain stability under demanding environmental conditions

The goal was to create a high-performance yet adaptable IP core suitable for critical aerospace applications.

The solution

A custom FPGA IP core was developed to handle high-precision time measurements and real-time data processing. The design focused on balancing accuracy, performance, and hardware efficiency, ensuring that the solution could operate reliably within constrained FPGA resources.

The architecture incorporates hardware-optimized statistical algorithms and validation mechanisms, enabling accurate and reliable processing of timing data. Compliance with the AXI4-Lite interface ensures seamless integration with processor-based systems, allowing efficient communication and control.

Technology stack:

- VHDL for FPGA design

- C/C++ for embedded components

- Vivado / Vitis for development and deployment

- HDL simulators for testing and validation

How it works

The IP core processes timing signals and performs real-time calculations directly in hardware, reducing latency and improving precision compared to software-based approaches.

Pipelining and resource optimization techniques enable high performance while maintaining efficient use of FPGA resources. Built-in validation mechanisms ensure data integrity, while standardized interfaces allow easy integration into broader system architectures.

Key capabilities:

- High-precision time measurement and processing

- Hardware-implemented statistical calculations

- Integrated data validation and error detection

- AXI4-Lite interface for system integration

- Optimized performance through pipelining and resource balancing

- Compatibility with multiple FPGA platforms

Impact on operations

The implementation of hardware-based timing and analysis significantly improved system precision and reduced processing latency. The IP core can be deployed across different FPGA platforms, enabling flexible integration into various aerospace systems without requiring extensive redesign.

Rigorous testing, including environmental validation, ensures stable performance under demanding operating conditions.

Business impact

The solution delivered measurable improvements across key areas:

- Improved timing accuracy, supporting more precise navigation systems

- Higher system performance, through hardware-based processing

- Reduced development costs, via compatibility with multiple FPGA platforms

- Enhanced reliability, validated under demanding conditions

- Scalable architecture, suitable for multiple aerospace applications

- Future-ready design, supporting evolving system requirements

The modular IP core can be reused and extended across different aerospace projects, providing a reliable foundation for future developments in navigation, communication, and autonomous systems.

We’ll review your goals, technical constraints, and opportunities to design a solution that fits your organization.

.avif)